#### FaultDetective Explainable to a Fault, from the Design Layout to the Software

Zhenyuan (Charlotte) Liu, Dillibabu Shanmugam and Patrick Schaumont WPI Vernam Lab

**CHES 2024**

April 2025

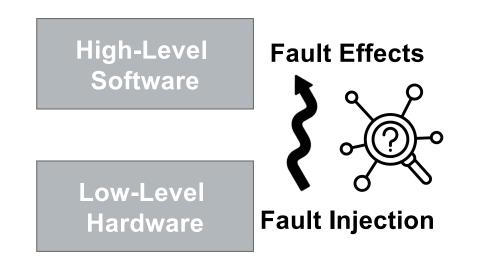

## What is Fault Root-Causing?

#### Explain Low-level Hardware Effects from High-level Software Observations

1

#### Why do we care?

- Three fault effects: correct output, no effects, faulty output

- > Unpredictable fault behavior

# Understand more than just the immediate output effects.

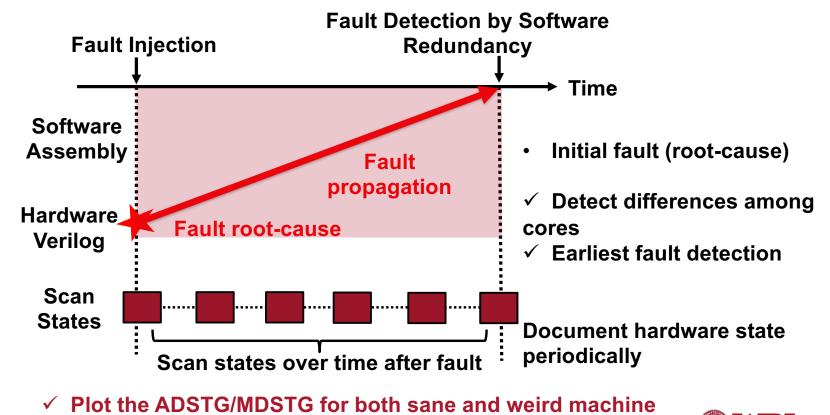

- ✓ Initial fault (the root-cause)

- ✓ Fault propagation from hardware to software

- ✓ Design improvements

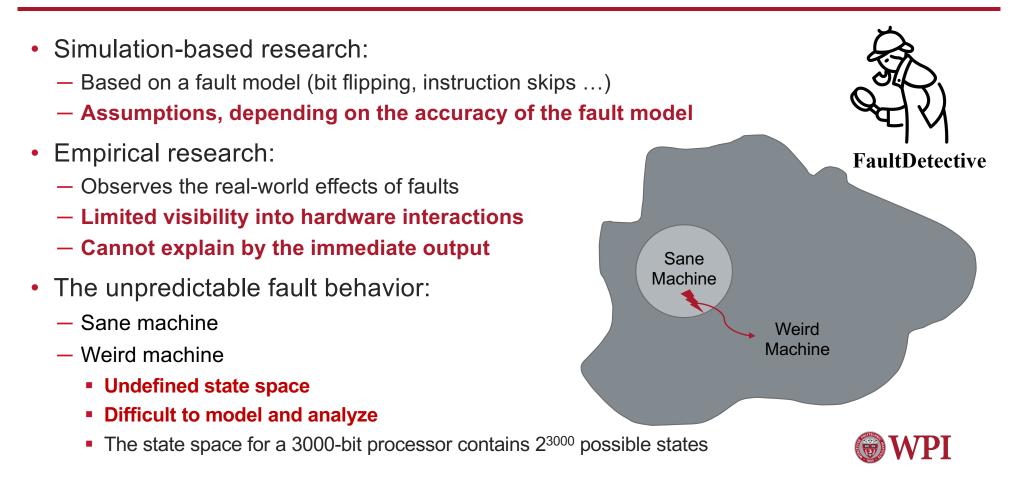

## **Current Research and Challenges**

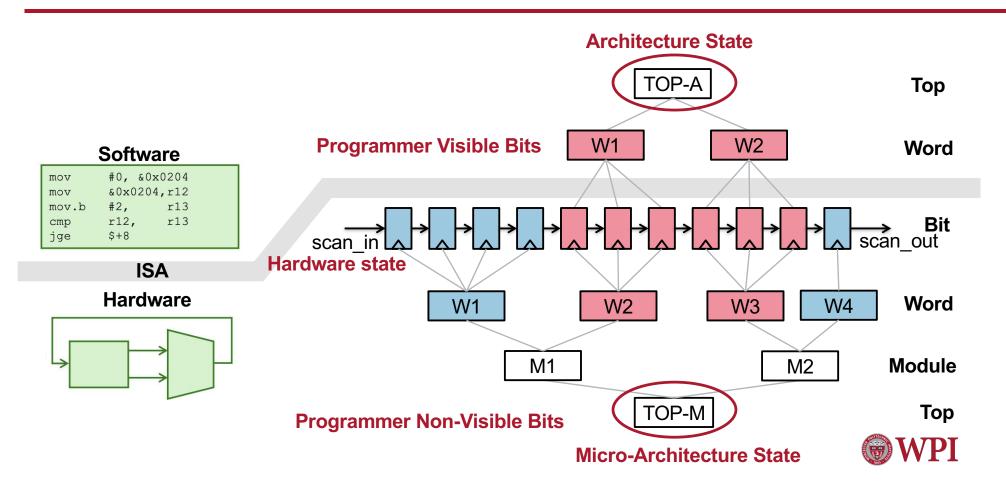

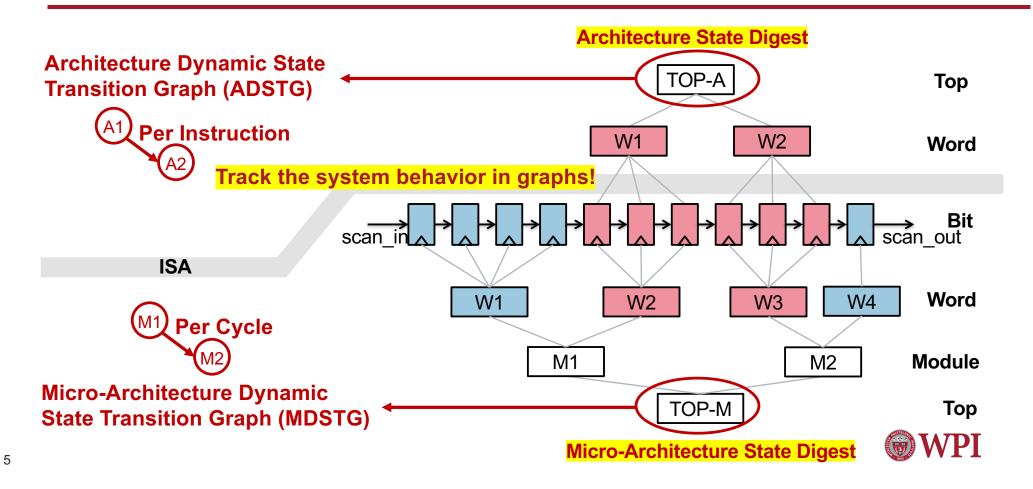

#### **Architecture and Micro-Architecture States**

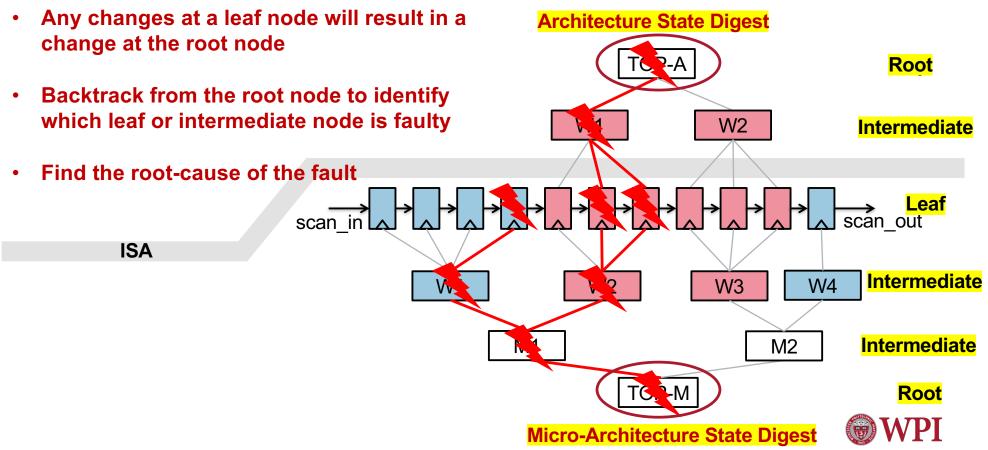

#### Hash Tree

\*please refer to our paper and find more details on the hash function.

4

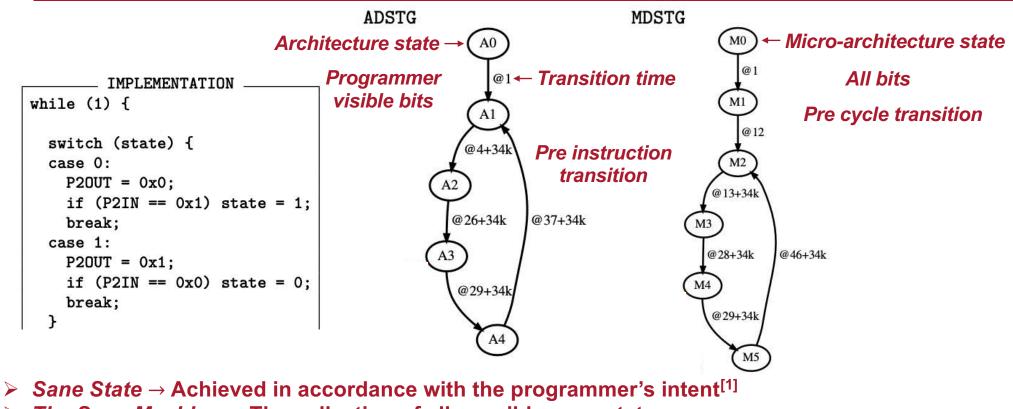

#### **Dynamic State Transition Graph**

#### **Dynamic State Transition Graph – Before Fault**

> The Sane Machine → The collection of all possible sane states

6

[1] Thomas Dullien. Weird machines, exploitability, and provable unexploitability. IEEE Transactions on Emerging Topics in Computing, 8(2):391–403, 2020.

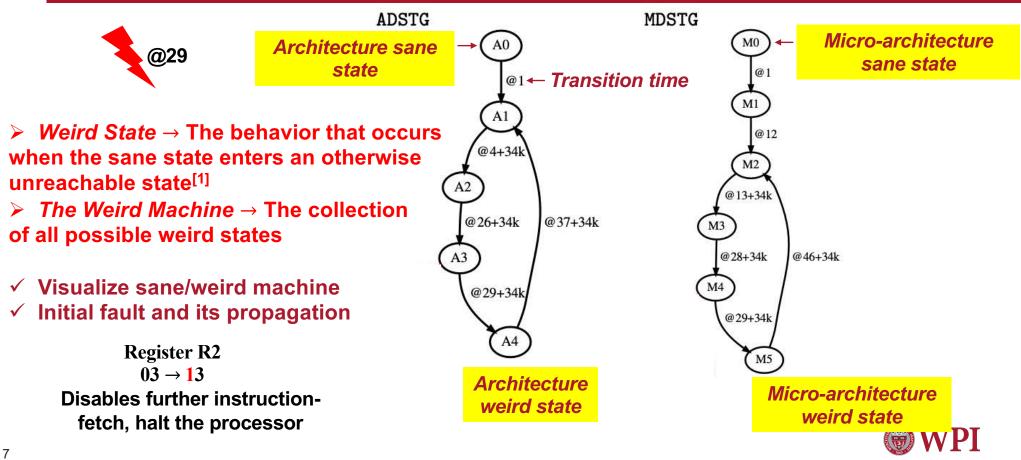

#### **Dynamic State Transition Graph – After Fault**

[1] Thomas Dullien. Weird machines, exploitability, and provable unexploitability. *IEEE Transactions on Emerging Topics III Computing*, o(2).991–403, 2020.

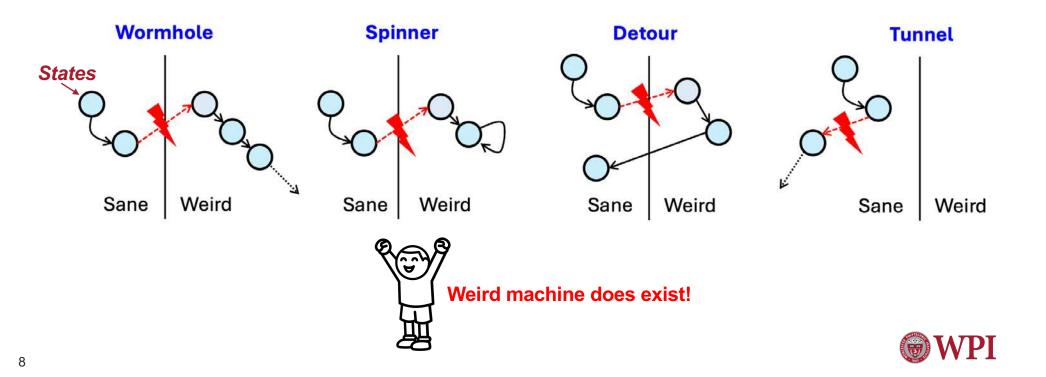

#### **Visualized Fault Patterns**

• Four fault patterns

#### Fault Root-Cause Analysis: FaultDetective

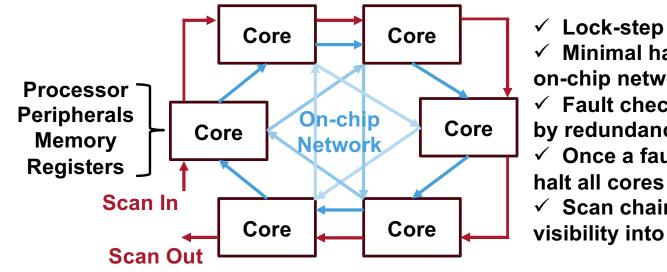

Hardware Redundancy + Scan Chain

Lock-step execution Minimal hardware in

on-chip network

✓ Fault checking in software by redundancy

✓ Once a fault is detected,

✓ Scan chain provides visibility into all flip-flop bits

#### Fault Root-Cause Analysis: FaultDetective

$\checkmark\,$  Apply to both simulation and measurement fault experiments  $\textcircled{\ensuremath{\mathbb{B}}} WPI$

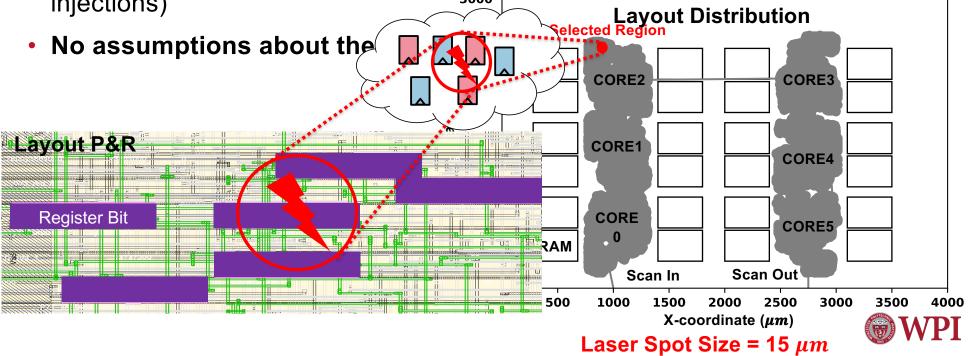

## **Layout-Aware Fault Analysis in Simulation**

• Realization in ASIC (six-core MSP430)

11

Implement real-world fault injection using layout data (laser and clock fault injections)

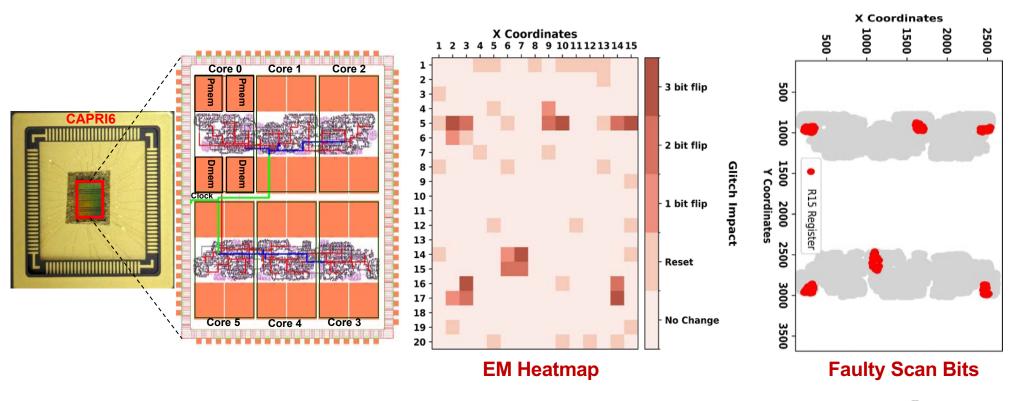

#### **Measurement Result with EM-fault Injection**

# **Any Questions?**

Thank you zliu12@wpi.edu dshanmugam@wpi.edu pschaumont@wpi.edu